大部份高速数位产品都使用时脉来进行系统定时同步,在一个时脉周期中必须完成一系列作业,包括一个逻辑深度内的所有门切换时延、晶片内部以及晶片之间的传播时延、互连引起的上升时间或充电时延、设立和保持时间,以及时脉与数据线之间的偏差等等。定时预算负责给每个时延源分配时间。本文介绍在满足功能要求的前提下,如何解决高速数位

PCB设计产品中定时预算、噪音预算和EMC测试要求所面临的挑战。

抖动指的是从一个周期到下一个周期之间,时脉或数据沿到达时间的变化。讯号传播时延源可能是随机性的(当这个抖动无法预测时),也可能是确定性的(当抖动量大小能够预测时,如当上升时间可与位周期相较时符号间干扰引起的抖动)。最后,PCB设计人员必须特定时预算增加一个‘裕量’,用来补偿无法淮确预测的所有其他因素。不确定性越多,意味着需要越大的裕量来确保产品正确工作。

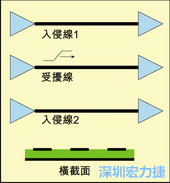

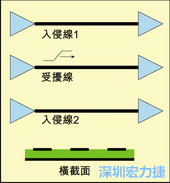

图1:包含三个数据位的简单汇流排。

图1:包含三个数据位的简单汇流排。

随着时脉频率的提高,时脉周期变得越来越短。PCB设计人员努力透过缩减定时预算中每个计画的时间分配来达到更高的时脉频率目标。PCB设计人员越能淮确预计定时预算中的每项因素,需要的裕量就越小。裕量减少之后,相应地就能允许在继续满足定时预算的前提下来缩短时脉周期。

有一种确定性抖动是来自于汇流排中相邻导线之间的串扰(即使在低损耗互连中也不例外)。采用能够预测串扰的互连模型和一种能够分析定时中串扰效应的优秀模拟器,PCB设计人员可以淮确预测串扰引起的确定性抖动,因而可以将抖动预算降到最低并减少裕量。透过认识串扰引起的抖动来源,可以将其影响降到最低,并采取成本与性能之间的折衷,使最终产品实现最最佳化。

串扰引起的抖动

当某根数据位导线上讯号的到达时间受到相邻数据位导线上同时出现讯号的影响时,便会发生串扰引起的抖动。

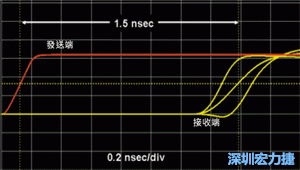

图2:受扰线上讯号的到达时间与模拟条件有关。

例如,考察一条包含三个数据位的简单汇流排(图1),每根数据位导线为一条9英寸长的50欧姆表层线(线宽和间隔都是5mil)。这条汇流排的中央数据位线将成为受扰线。PCB设计人员可以在三种相应的条件下模拟接收器端的讯号到达时间。可以模拟所有两根‘入侵线’,即受扰线两侧的相邻数据位线,分别让它们停止传输讯号、传输与受扰线相同的数据位,或传输与受扰线相反的数据位讯号。模拟结果显示,受扰线上讯号的到达时间与模拟条件有关(参见图2)。当其他数据位线停止传输讯号时,总时延为1.5ns左右,而其他两种条件下,根据汇流排上所传输的数据位模式,讯号的到达时间变化为±0.1ns,或者说约为总时延的7%。

当‘入侵线’与‘受扰线’驱动同样的数据位时,受扰线上的时延增大。当‘入侵线’上的数据位相反时,受扰线上的时延减少。如果在定时预算中忽略了这种形式的确定性抖动,产品就有可能出现故障(或者必须将所需的裕量增大)。藕合的容性或感性电流加到安静的导线上,将会影响到达时间和串扰引起的确定性抖动。虽然远端串扰和串扰引起的确定性抖动来源相同,但抖动幅度与总串扰无关,也与上升时间无关。讯号传播速度的变化导致了串扰引起的确定性抖动,PCB设计人员可以透过仔细设计来将其消除。设计一个包含大量串扰,却没有确定性抖动的系统是有可能的。

图3:当一条表层线导线与周围导线距离较远且相互隔离时,沿这条导线传播的讯号的一些场线将仅仅分佈在导线材料内部,而另一些场线则穿越空气分佈在讯号与返迴路径间。

确定性抖动与讯号速度

95%以上的电路板使用FR4材料。讯号透过一条均质传输线的传播时延仅仅与讯号传播时所面对的有效介电常数(kEFF)相关。如果kEFF约为3.5(FR4表层线中的kEFF可能就是这个值),则讯号的传播速度大致为:12英寸/ns/=6.4英寸/ns。例如,一条9英寸长导线的时延约为:长度/6.4英寸/ns=9/6.4=1.4ns。如果再加上因2pF输入门电容器引起的上升时间变长而导致的0.1ns左右的时延,就得到了约1.5ns的总传播时延。

由汇流排上位模式引起的kEFF的任何变化都将影响所有数据线上的讯号速度,而讯号速度影响传播时延,反过来又会对抖动产生影响。但相邻讯号线上的位模式怎么会影响受扰线上讯号所面对的kEFF呢?答案全在于边缘场线。

当一条表层线导线与周围导线距离较远且相互隔离时(图3),沿这条导线传播的讯号的一些场线将仅仅分佈在导线材料内部,而另一些场线则穿越空气分佈在讯号与返迴路径之间。延伸到导线宽度之外的场线称为边缘场线。在一条50欧姆的FR4表层线中,讯号与返迴路径之间的电容器约有一半是由边缘场引起的。

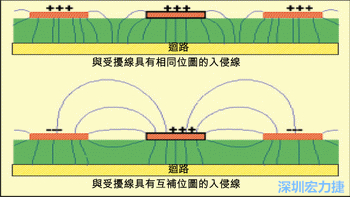

图4:不同边缘场的分佈。

相邻入侵讯号线的存在会影响受扰线的边缘场分佈,具体情况取决于入侵线上的位模式。当两根入侵线携带与受扰线相同的数据位时,所有三条讯号线上的电压相同,导线上方空气中的边缘场线很少。

当相邻入侵线上的数据位与受扰线上的数据位相反时,受扰线与入侵线之间有很大压差,并且存在许多边缘场。受扰线到返迴路径之间场线的分量越大(空气中的场线与导线材料中的场线相较),kEFF就越小。这些不同边缘场的分佈如图4所示。

当入侵线上的位模式与受扰线相同时,后者面对的kEFF增大,这将导致传播速度降低,时延变长。当入侵线上的位模式与受扰线相反时,受扰线上的kEFF减少,传播速度提高,时延变短。在前述的例子中,由于三条数据位线之间的藕合非常紧密,边缘场与kEFF变化引起的确定性抖动达±0.1ns(总时延为1.5ns)。

图5:对于受扰线的场线来说,介电系数一样,都等于导线条带的介电常数。

将确定性抖动降到最低

降低串扰导致的确定性抖动的一种途径是透过加大导线之间的间隔来降低边缘场的覆盖程度。例如,透过将导线间隔增大到线宽的两倍(这是为获得可接受的近端串扰而采取的一个常用设计规则),在总时延为1.5ns的情况下,可将确定性抖动降低到60ps以下,即总时延的4%。

减少受扰线与入侵线之间的间隔不仅会导致确定性抖动,还会引起串扰问题。为了降低串扰和抖动,导线间隔应尽可能加大,或至少两倍于线宽。但是,这种方法意味着降低印刷电路板的密度(可能导致成本增加)。PCB设计人员需要一种EDA工具来淮确预计串扰和确定性抖动,以评估成本与性能之间的折衷。一个整合二维场解决方案的模拟器不仅要自动考虑噪音效应,而且还应该将与串扰相关的确定性抖动纳入考虑。

消除确定性抖动

空气中边缘场的变化引起串扰导致的确定性抖动时,在同质介电分佈结构中将不会发生任何确定性的抖动,例如完全内嵌的表层线或带状线。在一个带状线几何中,受扰线与入侵线之间的边缘场可能发生紧密的相互作用,但无论边缘场如何分佈,对于受扰线的场线来说,介电系数一样,都等于导线条带的介电常数(图5)。

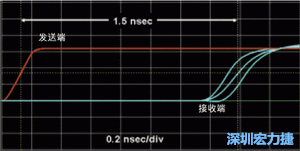

图6:入侵线无讯号、入侵线位模式与受扰线相同及相反三种情形下对受扰讯号到达时间的模拟结果。

对于极端情况,当导线间隔等于50欧姆带状线中的线宽时,kEFF总是等于导线材料的介电常数,而与入侵线上的位模式无关。当位模式改变时,受扰线上没有抖动。图6显示了入侵线无讯号、入侵线位模式与受扰线相同及相反三种情形下对受扰讯号到达时间的模拟结果。虽然受扰线上出现大量串扰电压,但受扰线上讯号的到达时间没有发生抖动。

在定时严格的设计中,PCB设计人员可以将所有对定时感应的讯号线佈设在掩埋的带状线层中,以消除抖动的一个来源,并降低所需的总定时预算。在选择整合有二维场解决方案的模拟器时,应该选择一种自动将噪音以及与串扰相关的确定性抖动纳入考虑的工具。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料