人类真是非比寻常的‘动物’,有时对于某些领域一知半解、自负和盲目自大比无知更危险──例如在电路设计时,这可能导致电路无法正常工作。当看到有经验的工程师犹豫不决时,某些人觉得自己还不如和没经验的人合作,甚至不明白为什么经验丰富的工程师反而进退两难。这里有三个例子,其中的简单分析能给

电路板设计者带来一些启发,使其于未来的设计中避免类似问题。

有些情况下,PCB设计人员往往错误理解元件的工作方式,以至于做出一些奇怪的假设,导致元件的错误使用。不幸的是,现在的工程院校几乎都把注意力集中在数位技术,甚至完全忽略了类比设计。缺乏类比设计经验的数位工程师只能从试验、失败中获得类比知识。这样的结果可能会使Rube Goldberg为之得意。谁是Rube Goldberg?他是一位曾经获得普立兹新闻奖(Pulitzer Prize)的漫画家,20世纪早期曾以一些荒诞的发明,将简单功能的机械组合复杂化,并以幽默戏谑的漫画讽刺人们如何将简单的事情极度复杂化而成名。

我们来考虑一些在类比工程师眼中非常可怕的情况,通常数位设计错误认知是:未意识到干净的电源和接地对电路设计有多么重要,连接电路时不考虑直流阻抗匹配。忽略实体法则的设计最终会导致系统失效。

别被表面现象迷惑

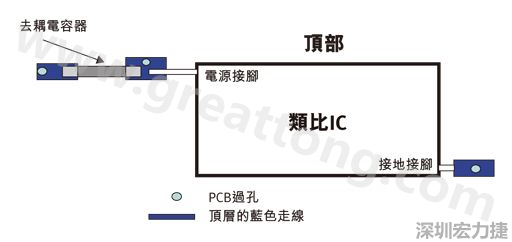

资料手册常常注明:“电源的去藕电容器要尽可能靠近IC的电源接脚放置。”如图1所示的印刷电路板(PCB),它们确实如此!

图1:一个印刷电路板(PCB)布局、IC和电容器。

该电路板用于视讯混合讯号,图1所示IC周围还存在其它元件,这些周边元件非常关键。这是一个四层板,讯号链路在最外两层,类比工程师通常将电源和接地分别布设在中间两层。元件包括高频类比/数位转换器(ADC)、数位/类比转换器(DAC)以及讯号处理电路。元件密度适中,没有球闸阵列(BGA)封装,不需要更多层或复杂布板。

测试这个设计时,我们发现视讯输出杂讯非常大。而且,大多数杂讯都来自一个IC。图1显示了电路板的顶层图,电源接脚测试到非常大的杂讯。当用一根很细的导线穿过去藕电容器的接地层过孔,连接到电路板的另一侧时,一条接脚(不在内部地层)消失在另一过孔,这将引发一些问题。

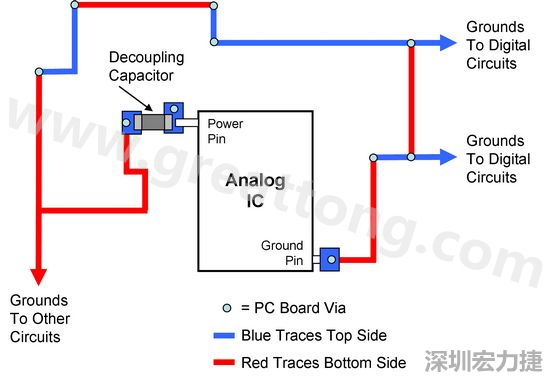

观察电路布局,突显出我们所感兴趣的节点,并可看到所有连线,如图2所示。

图2. 使用PCB设计软体得到的电路布局。

这些布线看起来是由数位电路自动布线工具完成的,电路板PCB设计人员可能并不具备类比电路设计经验。没有内部地层和电源层(参考AN4345有关接地技巧与合理布局)。

在没有设计经验的人眼里,这个电路完全正确,但是,因为所有地混杂在一起。这种连接对于直流没有问题,但在一定工作频率下,其等效电路上存在较大的寄生成分,如图3所示。

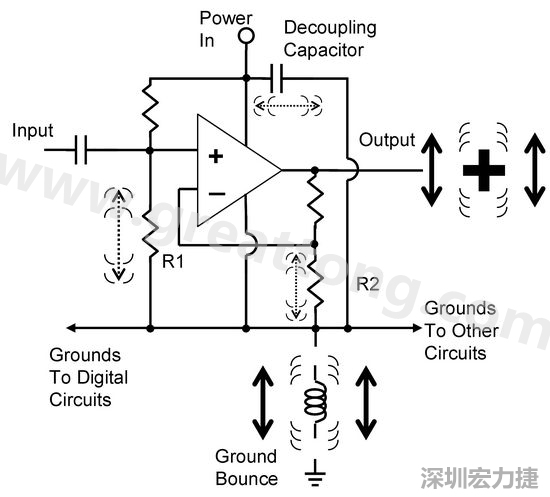

图3. 电路中‘地弹杂讯’的示意图。

图2中的每个通路和过孔都存在寄生电阻和电感。图3中,把这些分布寄生单元等效成与地串联的低频电感。图中,电感可以看作一个机械螺旋线电感;为方便解释,假设积体电路为运算放大器,但它可以是任何电路。

当其它电路的电流改变时,‘接地弹力’符号上方左右两端的数位电路及其它电路的杂讯会使电压上下波动。很多点都直接干扰到类比讯号:

1)杂讯通过R1藕合到运算放大器输入。

2)杂讯藕合到运算放大器的接地端。有人可能想借助‘电源抑制比’消除杂讯,但是,不要忘记,接地是其参考电位,这意味着杂讯将直接藕合到输出讯号。

3)杂讯通过R2藕合到运算放大器输入。

4)杂讯通过去藕电容器与R1电阻,藕合到运算放大器输入。

注意:电容器是一个双向元件,去藕电容器的作用是对电容器两侧的高频讯号取平均。如果电源汇流排上有杂讯,而接地非常干净,去藕电容器形成到电源的低阻迴路可有效降低杂讯。尽管如此,如果接地是高阻抗并存在很大杂讯,去藕电容器反而会把杂讯加到电源上。

如上所示,因为藕合杂讯讯号有相位差,杂讯藕合到运算放大器周围的各个节点,使得输出非常嘈杂。图中抖动所示,所有杂讯都会迭加到输出端。

输出也受运算放大器的非线性失真干扰,杂讯分量由此会产生和、差谐分波量,使整个频谱充满杂讯。

以上简单阐述良好的电源、接地层布局的重要性,对于没有类比设计经验的工程师,尤其值得注意。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料