WLP、WLCSP元件的焊点间距相当小,不同的焊垫设计也会左右焊点间的走线宽度限制,设计PCB时限制较多。

随着晶圆级晶片尺寸封装WLP、WLCSP,在微缩晶片的成效越来越显着,在电子产品的使用现况也有持续增加的现象,但WLP、WLCSP虽然可以在封装后晶片的尺寸可达到如同晶粒同等大小、具尺寸的绝佳优势,但在封装成品功能日趋复杂、接脚数目与设计要求越来越严苛,对

PCB设计即成为新的应用挑战...

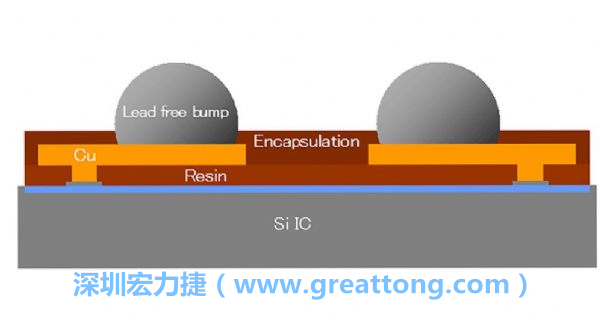

晶圆级晶片尺寸封装WLP(Wafer Level Packaging)、WLCSP(Wafer Level Chip Scale Package),其实是积体电路的一种封装方式,指的是在晶圆(Wafer)生产完成后直接于Wafer上进行封装、测试程序,当封装制作完成再进行切割成单个积体电路的封装制作方式。

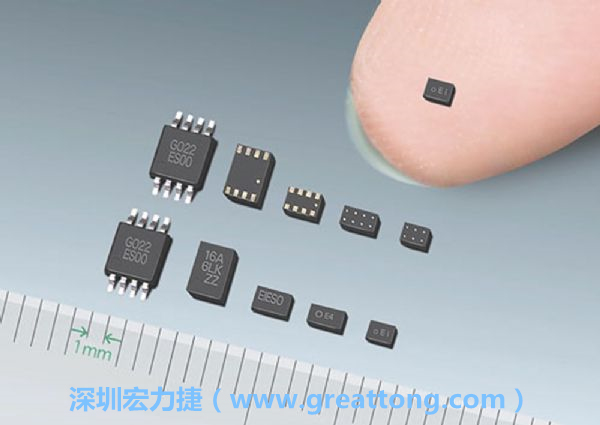

常规IC与WLP制作的封装设计元件,尺寸有极大的差异,WLP仅需晶粒尺寸就有相同的电气特性。

WLP为在晶圆阶段即进行元件封装,因此无常规IC的引脚、封装体填胶等空间需求,元件尺寸可以做到晶粒大小,因此PCB设计挑战更大。

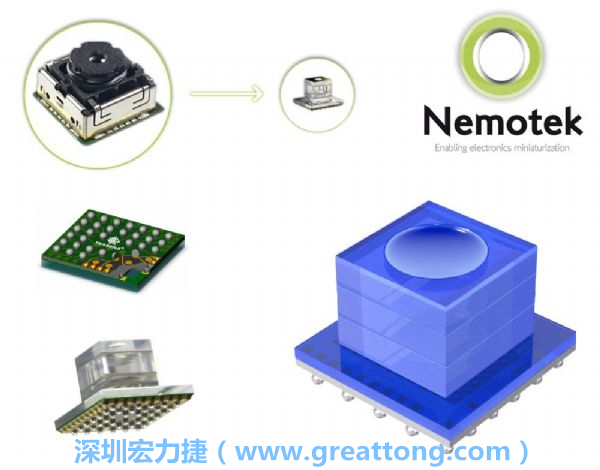

Nemotek利用WLP制作image sensor模组,搭配光学透镜设计,可让image sensor模组的占位面积大幅缩小,生产可用自动送料快速制作,节省产制成本。

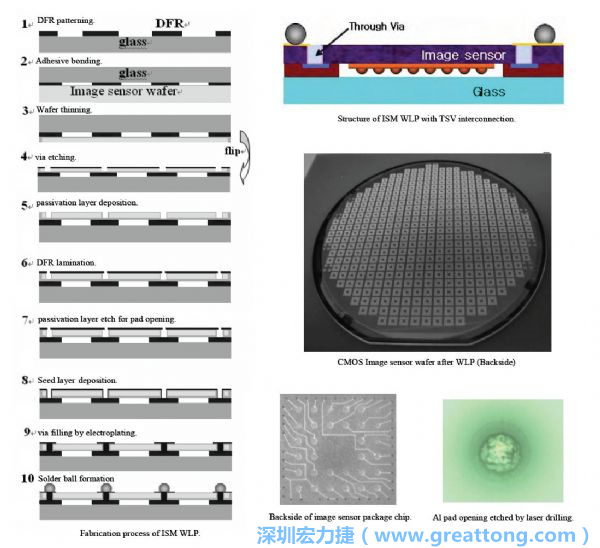

Samsung采用WLP形式制作的image sensor,直接利用晶圆级封装大幅缩减元件尺寸,元件可做到极薄与最小占位面积。

WLP、WLCSP有别于晶圆切割成晶粒、再经由封装中打线追加引脚的积体电路制作方式,正因为少了封装的体积占用,WLP、WLCSP可以达到相同的IC应用功能,却只要如同切割后晶粒大小的占位面积,而WLP、WLCSP制成单颗IC过程中,亦不用如同一般IC需进行打线、填胶,在发展小型化或超小型的微缩设计产品方案时,WLP、WLCSP封装设计方式的IC应用,可以达到极佳的产品微缩效益,加上WLP、WLCSP元件本身具备极佳电性(因为少了打线与引脚),针对高速传输应用的元件使用效益更高,元件因可在晶圆上加工,也缩减了IC的繁琐制程。

WLP、WLCSP体积小、重量轻

但问题来了,WLP、WLCSP虽然体积相当小,随着常规IC的接脚数目越来越多,WLP、WLCSP形式封装使用的球距要求趋于严苛,但对于电路设计所需要的电性,基本上跟一般IC所需的电性支援并无不同,但WLP、WLCSP的尺寸已经缩小到晶粒尺寸,加上PCB可与WLP、WLCSP连接的接点、线路都极小,在PCB的设计方案并不如一般IC应用方案来得轻松。

至于,采用行晶圆级封装,目的是为了降低解决方案的成本与整体尺寸,但连带的当导入晶圆级封装后,PCB的成本势必会因为采用行晶圆级封装,必须进行对应的线路与打孔制程改善,让PCB特性可以与WLP、WLCSP元件充分搭配,而不会出现连接上的问题。尤其在设计方案中使用了WLP、WLCSP后,PCB会变得更趋复杂,角色也会显得较为重要,设计时需审慎规划,避免PCB的质量导致终端产品出现稳定度问题。

当我们在进行载板设计时,基本上在现有的设计产品中,可用的载板面积已经越来越小,而工程师又得面对持续缩小的设计要求,例如,穿戴型的电子产品,如手表型、行动电话的电子电路,可使用的载板空间极度珍贵,而为了降低终端设计采用行的PCB面积,导入如WLP、WLCSP更小的IC封装,已经是无法避免的设计趋势。

在晶圆阶段进行元件封装 大幅节省载板占位面积

由于WLP、WLCSP封装是直接建立「硅」基板上的封装制程,IC基本上是不需使用焊线,对高频元件来说可直接获得更好的高频电性,达到缩短周期时间效益,而因为封装可以在晶圆厂完成,同时可节省封装成本,但对于工程师来说,设计方案也必须朝向降低成本方向考量,要搭配WLP、WLCSP元件同时PCB成本也必须限制在一定程度范围,必须注意权衡设计,或采用取线路布局对应。

一般来说,进行导入WLP、WLCSP元件,在执行PCB线路布局规划前,工程师必须先取得WLP、WLCSP的占位面积(即封装后尺寸),同时对WLP、WLCSP元件确认尺寸/接点误差、接点间距等元件关键讯息,开始进行电路布局、处理元件摆位,即可利用取得的元件参数进行设计规划,而因应WLP、WLCSP的尺寸与接点变得更小,还须考量适用IC接脚的焊垫设计方案。

PCB需针对SMD、NSMD形式做对应微调

可搭配WLP、WLCSP的焊垫类型,可以使用Solder Mask Defined(SMD)与Nonsolder Mask Defined(NSMD)。焊罩定义型SMD焊垫,其设计方式为利用焊罩定义焊球、将被焊接之焊垫面积,这种设计方案可以减少焊垫于焊接或除焊过程,可能被拉高的可能性,但SMD形式的缺点是,SMD减少了与锡球连接之铜表面的表面积,同时减少相邻焊垫间的空间,这会让焊垫间的走线宽度受限,也可能造成PCB的导通孔使用弹性。在多数设计方案中,较被常用的仍是SMD设计方案,因为SMD的焊垫可以有较佳的焊锡连接特性,在制作过程中可让焊锡和焊垫整个结合在一起。

至于非焊罩定义型焊垫(NSMD),设计方法是利用铜进行焊锡凸块焊接之焊垫面积定义,这种设计方案可提供更大的表面积,来使PCB与锡球进行连接,同时NSMD相较SMD设计形式,亦提供焊垫与焊垫间更大的绝缘间距,可允许更宽的焊垫间走线间距,对于PCB的导通孔的使用弹性更高,但NSMD若在进行焊接、除焊等操作过程很容易造成焊垫被拉高。

针对间距需特别考量

间距尺寸的考量也相当重要,尤其是PCB在采用行SMD或NSMD形式,不同的方案在预留的间距尺寸也会略有差异,而间距尺寸指的是锡球间的距离,此为两个锡球的圆心距离,而间距尺寸越大,代表焊垫与焊垫之间可用来进行布线的线路空间越大。

对于0.5毫米的设计方案中,由于间距较大,提供更多的走线空间,或是设计时可以使用较宽、铜材料较多线路,这表示可在走线驱动更高的传输电流,绝缘距离也可以轻松完成设计。对于绝缘距离,一般需检视所要求的设计规范,一般绝缘距离为3~3.5密尔(mil)。相较0.4毫米的间距宽度设计,就相对设计更为困难,因为可用的布线空间弹性限制更多,而可用的绝缘间距也会因为间距缩小而同时减少,这代表可在线路中使用的铜变少了,传输的驱动电流也会对应减少。

在PCB布线方面,因为WLP、WLCSP元件特性,可用的锡球间距相当小,基本上是无法使用机械开孔设备进行PCB开孔,因为机械开孔的孔径过大,开孔过程也可能让PCB上较薄的线路因为开孔过程误差受损。而在有使用WLP、WLCSP元件的PCB,由于线路较紧密许多,也会改用成本较高的雷射钻孔来处理导通孔(laser-drilled via)。

一般来说,只有在中、高单价的终端产品,才会使用高成本的雷射开孔PCB制作方案,而会用雷射开孔也会同时搭配多层板进行制作,成本会较四层板高许多,对于一些低成本应用方案,使用多层板、雷射开孔设计方案基本上是较为不划算。而另一种相对不常见的设计方案,是采用行交错锡球凸块阵列(staggered bump array)之WLP元件,利用做在WLP晶片上使锡球交错,让产品开发者争取更多可用空间来进行PCB线路布局。但事实上WLP搭配staggered bump array的成本相当高,同时,此方案必须在WLP、WLCSP元件进行开发时就同步进行考量,在元件制作难度较高,也会因此提高元件成本。

结语

晶圆级晶片尺寸封装WLP、WLCSP元件,对于缩小终端产品尺寸具有极佳的改善效益,但换来的是PCB设计方案也必须同步升级,搭配高密度多层板、雷射开孔的精密制程进行开发,原本自IC元件省下的载板空间、元件成本,会部分转嫁到PCB设计与后段的量产制作上,而采用行更小的元件,在产品后段的产线打件、加工或维修,也会造成部分较难施作的操作问题,这在进行相关设计前都必须一一考量。

WLP、WLCSP元件为晶圆级晶片尺寸封装,最终IC的外观、尺寸之封装大小几乎与晶片是相同的,晶圆级的晶片尺寸封装优点相当多,像是元件尺寸大幅缩小,减少了常规IC应有的面积、厚度,元件的重量更轻,元件可利用更适应大量产线生产的自动化上料打件制作,可降低整体生产成本,甚至WLP、WLCSP元件本身针对高频应用的电气特性表现会更好,应用在需要轻量化、缩小体积的行动装置,如手机、笔记型电脑、穿戴式智慧产品,都可以用来大幅缩减载板面积、产品重量的重要手段。WLP、WLCSP元件若可以在导入前即针对晶圆级封装技术做更多整合,如搭配重新布线层技术、凸块等改善WLP、WLCSP元件设计,可以让WLP、WLCSP元件与PCB的搭配整合在设计上更为轻松。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料