深圳宏力捷是拥有平均超过10年工作经验PCB设计团队的PCB设计公司,能熟练运用市场主流PCB设计软件,专业高效沟通保证PCB设计进度。接下来为大家介绍PCB板设计中匹配电阻的作用。

一、PCB设计阻抗匹配

PCB设计阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。根据接入方式PCB设计阻抗匹配有串行和并行两种方式;根据信号源频率PCB设计阻抗匹配可分为低频和高频两种。

高频信号一般使用串行PCB设计阻抗匹配

串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度成反比。在嵌入式系统中,一般频率大于20M的信号且PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据和地址总线信号等。串行匹配电阻的作用有两个:

1. 减少高频噪声以及边沿过冲。如果一个信号的边沿非常陡峭,则含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。串联电阻与信号线的分布电容以及负载输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。

2. 减少高频反射以及自激振荡。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。

并行PCB设计阻抗匹配又叫“终端PCB设计阻抗匹配”

一般用在输入/输出接口端,主要指与传输电缆的PCB设计阻抗匹配。例如,LVDS与RS422/485使用5类双绞线的输入端匹配电阻为100~120Ω;视频信号使用同轴电缆的匹配电阻为75Ω或50Ω、使用扁平电缆为300Ω。并行匹配电阻的阻值与传输电缆的介质有关,与长度无关,其主要作用也是防止信号反射、减少自激振荡。

值得一提的是,PCB设计阻抗匹配可以提高系统的EMI性能。此外,解决PCB设计阻抗匹配除了使用串/并联电阻外,还可使用变压器来做阻抗变换,典型的例子如以太网接口、CAN总线等。

二、零欧姆电阻

1. 最简单的是做跳线用,如果某段线路不用,直接不焊接该电阻即可(不影响外观)。

2. 在匹配电路参数不确定的时候,以零欧姆代替,实际调试的时候,确定参数,再以具体数值的元件代替。

3. 想测某部分电路的工作电流时,可以去掉零欧姆电阻,接上电流表,这样方便测量电流。

4. 在PCB设计布线时,如果实在布不过去了,也可以加一个零欧姆的电阻起跨接作用。

5. 在高频信号网络中,充当电感或电容(起PCB设计阻抗匹配作用,零欧姆电阻也有阻抗)。充当电感用时,主要是解决EMC问题。

6. 单点接地,例如模拟地与数字地的单点对接共地。

7. 配置电路,可以取代跳线和拨码开关。有时用户会乱动设置,易引起误会,为了减少维护费用,应用零欧姆电阻代替跳线等焊在板子上。

8. 系统调试用,例如将系统分成几个模块,模块间的电源与地用零欧姆电阻分开,调试阶段发现电源或地短路时,去掉零欧姆电阻可缩小查找范围。

上述功能也可使用“磁珠”替代。零欧姆电阻与磁珠虽然功能上有点类似,但存在本质差别,前者呈阻抗特性,后者呈感抗特性。磁珠一般用在电源与地网络中,有滤波作用。

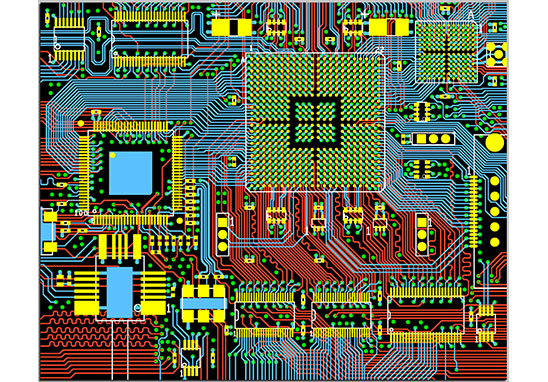

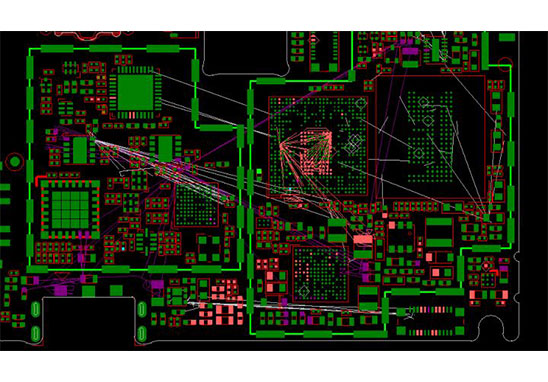

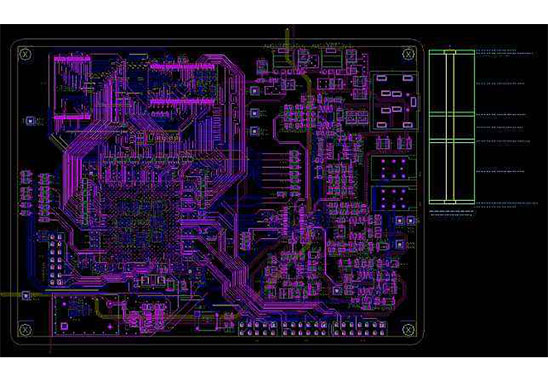

PCB设计能力

最高信号设计速率:10Gbps CML差分信号;

最高PCB设计层数:40层;

最小线宽:2.4mil;

最小线间距:2.4mil;

最小BGA PIN 间距:0.4mm;

最小机械孔直径:6mil;

最小激光钻孔直径:4mil;

最大PIN数目:;63000+

最大元件数目:3600;

最多BGA数目:48+。

PCB设计服务流程

1. 客户提供原理图咨询PCB设计;

2. 根据原理图以及客户设计要求评估报价;

3. 客户确认报价,签订合同,预付项目定金;

4. 收到预付款,安排工程师设计;

5. 设计完成后,提供文件截图给客户确认;

6. 客户确认OK,结清余款,提供PCB设计资料。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料