在高速数字电路设计中,PCB(印刷电路板)的性能直接影响信号的完整性和系统的稳定性。阻抗匹配是高速PCB设计的关键环节,对于确保信号无损传输、减少反射、提高信号质量至关重要。深圳宏力捷电子作为专业的PCB设计公司,致力于提供多层、高精密/BGA封装以及盲孔/埋孔的PCB设计服务。

阻抗匹配的概念

阻抗匹配是指信号源的输出阻抗与负载阻抗相等,以实现最大功率传输或最小信号失真。在高速PCB设计中,主要是保证传输线(如微带线、带状线)的特性阻抗与连接的芯片引脚、过孔、连接器等的阻抗一致,从而减少信号反射和确保信号质量。

阻抗匹配的必要性

在高速信号传输过程中,阻抗不连续会导致信号反射,进而引起信号失真、上升沿变缓、甚至振铃效应,严重时可导致系统误操作。因此,阻抗匹配是确保信号完整性、提高系统稳定性的基石。

特性阻抗的计算

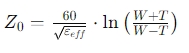

特性阻抗(Z0)由传输线的物理结构(如宽度、厚度、介电常数等)决定,其计算公式根据不同类型的传输线而异。例如,微带线的特性阻抗计算公式为:

其中,W是线宽,T是导体厚度, 是有效介电常数。准确计算特性阻抗需要使用专业的PCB设计软件,这些软件通常内置了各种传输线模型的计算工具。

是有效介电常数。准确计算特性阻抗需要使用专业的PCB设计软件,这些软件通常内置了各种传输线模型的计算工具。

实现阻抗匹配的方法

1. 控制线宽和间距:通过调整PCB上导线的宽度、间距以及介质层的厚度,可以精确控制特性阻抗。设计时需根据计算结果调整这些参数,确保与目标阻抗匹配。

2. 使用阻抗控制层叠:选择合适的板材和确定层叠结构对阻抗控制至关重要。合理安排电源层、地层的位置和介质材料,可以优化整个板子的阻抗特性。

3. 终端匹配:在信号线的末端添加匹配元件(如电阻、铁氧体磁珠、巴伦等),可以吸收反射波,减少信号反射。常用的终端匹配方法有串联终端电阻、并联终端电阻、AC终端匹配等。

4. 差分对设计:对于高速差分信号,通过保持两根信号线的长度、线宽、间距等参数严格对称,可以自然形成较好的阻抗匹配,同时利用差分信号的共模抑制特性进一步降低噪声干扰。

5. 仿真验证:在设计完成后,利用仿真软件(如HyperLynx、ADS等)对PCB的信号完整性进行仿真分析,检查阻抗匹配情况及信号传输质量,必要时根据仿真结果调整设计。

阻抗匹配的挑战与解决方案

阻抗匹配是一个涉及多方面考虑的复杂过程,需要设计师对电路理论、材料特性、设计软件应用等有深刻的理解。以下是一些常见的挑战和解决方案:

1. 多层板设计:在多层板设计中,需要精确计算每一层的阻抗。解决方案是使用专业设计软件,并仔细选择和排列每层的材料和厚度。

2. 高速信号的交叉干扰:高速信号可能会产生交叉干扰。解决方案是通过差分对设计和适当的层叠结构来减少干扰。

3. 制造公差的影响:制造过程中不可避免的公差可能会影响阻抗。解决方案是与制造商密切合作,确保设计参数在制造公差范围内。

结论

高速PCB设计中的阻抗匹配是确保信号完整性和系统稳定性的关键步骤。通过精确计算、精心布局、合理选材和终端匹配等手段,可以有效实现阻抗匹配,从而保证高速信号的高质量传输,提升整个电子系统的性能和可靠性。深圳宏力捷电子凭借专业的设计团队和先进的设计工具,致力于为客户提供高质量的PCB设计服务,确保每一个项目的成功实施。

深圳宏力捷推荐服务:PCB设计打样 | PCB抄板打样 | PCB打样&批量生产 | PCBA代工代料

是有效介电常数。准确计算特性阻抗需要使用专业的PCB设计软件,这些软件通常内置了各种传输线模型的计算工具。

是有效介电常数。准确计算特性阻抗需要使用专业的PCB设计软件,这些软件通常内置了各种传输线模型的计算工具。